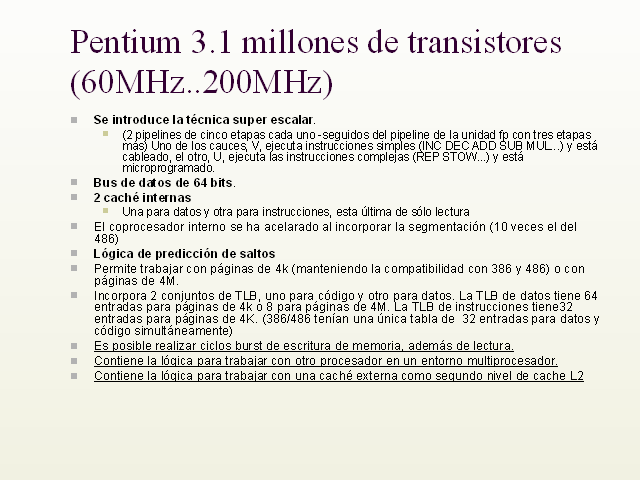

Pentium 3.1 millones de transistores (60MHz..200MHz)

Se introduce la técnica super escalar.

(2 pipelines de cinco etapas cada uno -seguidos del pipeline de la unidad fp con tres etapas más) Uno de los cauces, V, ejecuta instrucciones simples (INC DEC ADD SUB MUL…) y está cableado, el otro, U, ejecuta las instrucciones complejas (REP STOW…) y está microprogramado.

Bus de datos de 64 bits.

2 caché internas

Una para datos y otra para instrucciones, esta última de sólo lectura

El coprocesador interno se ha acelarado al incorporar la segmentación (10 veces el del 486)

Lógica de predicción de saltos

Permite trabajar con páginas de 4k (manteniendo la compatibilidad con 386 y 486) o con páginas de 4M.

Incorpora 2 conjuntos de TLB, uno para código y otro para datos. La TLB de datos tiene 64 entradas para páginas de 4k o 8 para páginas de 4M. La TLB de instrucciones tiene32 entradas para páginas de 4K. (386/486 tenían una única tabla de 32 entradas para datos y código simultáneamente)

Es posible realizar ciclos burst de escritura de memoria, además de lectura.

Contiene la lógica para trabajar con otro procesador en un entorno multiprocesador.

Contiene la lógica para trabajar con una caché externa como segundo nivel de cache L2

Pentium pro. 5.5 millones de transistores. (150MHz..200MHz)

introduce el concepto de dual cavity: Incluye la L2 en el mismo empaquetamiento físico, aunque técnicamente está separada del procesador. 256Kb. Manteniendo la caché internas (8k+8k).

Se aproxima en concepto a los procesadores RISC: Las instrucciones tradicionales 8086 se decodifican en subinstrucciones internas que son las que realmente se ejecutan en los cauces de segmentación. Todas las instrucciones internas tienen un formato triádico lo que conlleva la introducción de una gran cantidad de registros internos en los que mantener los datos con los que trabajan estas instrucciones.

Es un procesador supersegmentado porque los cauces se desarrollan en 12 ( frente a las cinco hasta ahora) etapas

Es un procesador superescalar porque contiene varias unidades de ejecución simultánea.

Admite ejecución fuera de orden (especulativa), aunque no en accesos de escritura a memoria.

Gestiona la predicción de los saltos.

Tecnología MMX. (extensión multimedia)

Se refiere a una posible extensión de las capacidades de los procesadores para adaptarse mejor a entornos multimedia. Ello se logra incorporando funciones propias de un DSP (Proceso digital de señales)

mmx del procesador comparte registros con la FPU

Register aliasing: La misma batería de registros llamadas con diferente nombre

Maneja 4 tipos de datos sobre un registro de 64 bits.

Cuádruple palabra 64 bits

Doble palabra empaquetada 2×32 bits

Palabra empaquetada 4*16 bits

Byte empaquetado 8×8 bits

Incorpora hasta 57 nuevas instrucciones específicas mmx.

Pentium II (233..450MHz )

Integra una caché L2 de 256 Kbytes

Asociativa 4 vías 32 bytes por bloq ue.

Ejecución dinámica

MMX

Coprocesador matemático integrado

Caché L1 de instrucción (16 K) y datos (16 K)

Asociativa 4 vías con bloque de 32 bytes

Con Registros programables de rangos de direcciones cacheables

Pentium III (500…1GHz)

Añade extensiones Streaming SIMD

Orientado a mejorar el rendimiento de gráficos 3D

Arquitectura Dual Independ Bus (desde Pentium Pro)

Acceso a caché L2 independiente del acceso al bus externo. Yendo a mayor velocidad el bus de caché

Soporte para Multiprocesamiento

2 procesadores

Pentium 4 (..3.8GHz)

Intel NetBurst® Microarchitecture

Hyper-Threading Technology

Hyper-Pipelined Technology

1066MHz, 800 MHz, 533 MHz or 400 MHz System Bus

Level 1 Execution Trace Cache

Enhanced Intel SpeedStep® Technology

Intel® Enhanced Memory 64 Technology (Intel® EM64T)F

Página anterior Página anterior |   Volver al principio del trabajo Volver al principio del trabajo | Página siguiente  |